Introducing MOReal™

A tool that greatly reduces massive netlists generated by extraction tools in analog, RF, and digital IC design flows.

- A high reduction ratio up to 1000x.

- Highly accurate reduced model with a pre-specified error.

- Very fast, massively parallel reduction algorithm.

MOReal Supplemental Materials

MOReal™ User Guide

Download FileMOReal™ brochure

Download FileMOReal™ Additional Contents

Download FileFAQ

What is MOReal?

expand_more

MOReal is a state-of-the-art model order reduction tool for reducing extracted parasitic interconnects. With its unique capabilities, electromagnetic experts, as well as IC designers, can use MOReal to reduce their huge parasitic netlists very quickly and then perform different analyses and simulations faster than before using the equivalent reduced circuit generated.

Is MOReal a modeling tool?

expand_more

No, MOReal does not model or extract parasitic interconnects. MOReal objective is reducing parasitic netlists after performing a parasitic extraction process using tools such as Calibre, RaptorX, Quantus, Star RC … etc. MOReal applies a novel mathematical model order reduction algorithm that takes massive networks of linear parasitic instances and reduces them to smaller ones while maintaining the behavior and characteristics of the original circuit.

What types of technology are supported by MOReal?

expand_more

MOReal handles parasitic circuits produced from all of the technology nodes. MOReal is independent from technology nodes because it operates after the extraction process, while extracted tools are the ones responsible for modeling parasitic effects.

What is the Extraction operation? And why is it essential?

expand_more

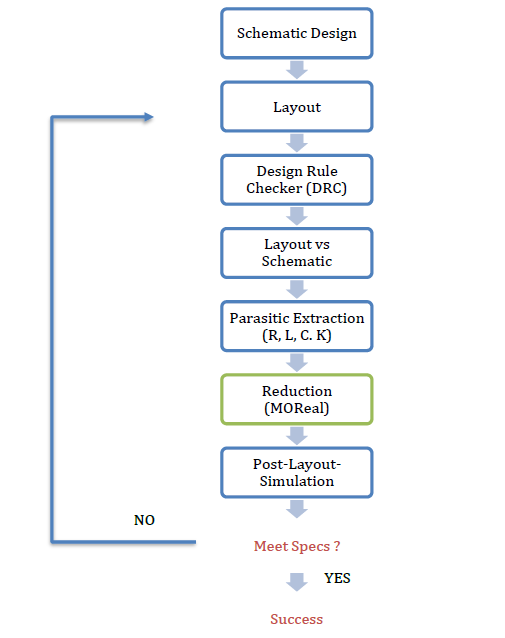

After finishing the layout of analog or digital circuit, engineers are required to do design rule checks (DRC), checking layout vs. schematic (LVS) and model the parasitic behavior of the added interconnects in the layout. The process of modeling the electromagnetic effects of interconnects is called Extraction. Extraction tools model these parasitic effects by adding linear instances like resistors, capacitors, inductors, and mutual inductor to the circuit. These parasitic effects have a significant impact on delay, energy consumption, power distribution, and introducing noise that affects the reliability of the chip.

What is Model Order Reduction? And why is it needed?

expand_more

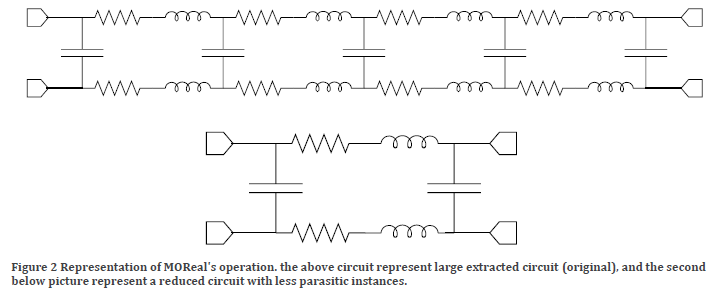

The market always pushes towards building fast chips that can perform multiple operations at once; therefore, industry leaders are required to construct complex chip designs operating at very high frequencies. However, extracting these parasitic effects of the chip results in a gigantic circuit that contains a large number of parasitic instances, and it becomes hard and sometimes impossible to simulate this huge circuit to study delay, noise, power consumption, and other important analyses. Reducing this gigantic circuit to a small one while preserving all of its properties and characteristics is the function of “Model Order Reduction (MOR).” MOReal is a MOR tool that can reduce large circuits full of parasitic instances to a smaller circuit ready for post-layout simulations and analyses. As an example, please, refer to the next figure.

Does MOReal require any PDK files or layout files to run?

expand_more

No, MOReal does not require any PDK files or layout files to run. MOReal only requires all of the parasitic netlist files produced by the extraction tools.

What are the input files required by MOReal?

expand_more

After finishing the layout cycle and running parasitic extraction, MOReal only requires all of the parasitic netlist files produced by the extractor tool in your design flow to be provided to MOReal as explained in the “How to use MOReal section” section.

What is the frequency range supported by MOReal?

expand_more

MOReal supports reducing circuits from DC to the terahertz range. MOReal supports different model order reduction modes based on what frequency the user is interested in. MOReal takes sparameter analyses as an approach for making sure that the reduced network matched the extracted netlists. Some extraction tools produce reduced circuits that either work from DC, zero frequency, to a high operating frequency, which is called a wideband extraction or operate at one frequency point, which is a narrowband extraction. MOReal supports reducing these two types of extracted circuits.

Is MOReal compatible with other EDA tools?

expand_more

Yes, MOReal produces an output file written in the format that can be read by analog and digital circuit simulators such as Cadence Virtuoso, Multisim … etc.

MOReal fits in the analog and digital design flows as shown below.

MOReal in Analog design

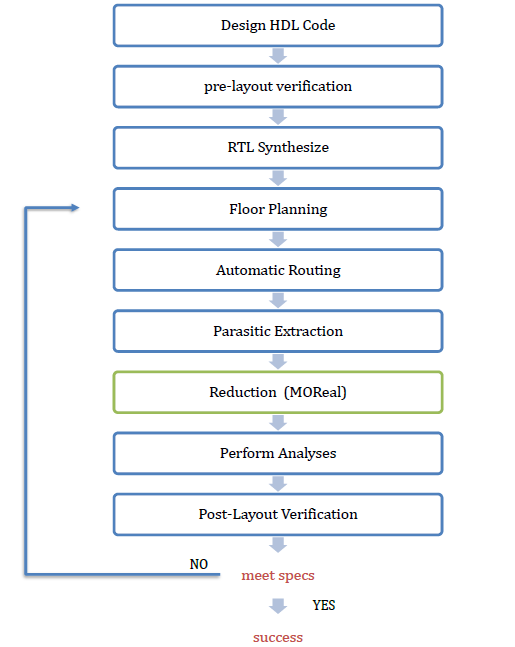

In digital design, parasitic extraction is essential for performing static timing analyses to get the network delay, noise analyses, crosstalk analyses, signal integrity checks, logic simulation doing logic simulations, IR analyses, and substrate noise analyses.

MOReal in Digital design flow:

How MOReal’s output is going to simulate faster?

expand_more

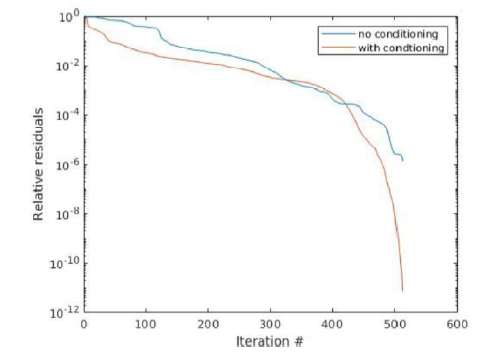

MOReal does more than reducing nodes and elements of the input circuits. Not only it performs reduction of nodes and elements in a unique novel way enabling reaching very high reduction ratios without sacrificing accuracy, it also produces a reduced circuit that exhibits a better conditioning property. The graph below shows the importance of conditioning enhancement on decreasing the time of the iterative solvers employed by circuit simulators; therefore, MOReal’s reduced circuit simulates very fast on circuit simulators.

Figure 3: The graph shows that systems with better conditioning enhancement performs better than other systems without conditioning.

GET IN TOUCH!

We'd love to hear from you! Please fill out the form below to contact us.

5834 Westslope Dr, Austin, TX, 78731

info@suiteratech.com